module do2(rst,clk,cout);

input rst,clk;

output [7:0]cout;

reg [2:0]D;

reg [19:0]count;

assign cout=out(D);

always@(posedge clk) begin

count = count+20'd1;

if(rst) begin

D<=3'b0;

end

else if(count==20'd100000)begin

D[0] <=D[1];

D[1] <=D[2];

D[2] <= D[0] ^D[2];

end

end

function [7:0]out;

input [2:0]in;

begin

case(in)

3'b000 : out =8'b11111100 ;

3'b001 : out =8'b01100000 ;

3'b010: out =8'b11011010 ;

3'b011 : out =8'b11110010 ;

3'b100 : out =8'b01100110 ;

3'b101 : out =8'b10110110 ;

3'b110 : out =8'b00111110 ;

3'b111 : out =8'b11100100 ;

endcase

end

endfunction

endmodule

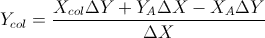

I write the verilog programming code using QuartusII. I want to make a random number generation operation. Linear Feedback Shift Register is used to generate random number. But, I don't know why the random pattern is same. The result of operation like this 8 5 4 2 7 .... 8 5 4 2 7. How to solve these problem? Please refer your opinion.